对标AMD、Intel!中国首个小芯片标准发布

导读: 在近期激烈的全球竞争中,国产芯片产业迎来一项重要利好,中国首个原生Chiplet 技术标准正式审定发布!在12月16日举办的“第二届中国互连技术与产业大会”上,由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布

科技巨头率先成立了Chiplet标准联盟

整个芯片产业其实很早就做好了迎接Chiplet技术的准备。在今年3月,英特尔、AMD、ARM、高通、台积电、三星、日月光、Google云、Meta(Facebook)、微软等十大行业巨头联合成立了Chiplet标准联盟(UCIe 联盟),正式推出了通用芯粒互连技术(Universal Chiplet Interconnect Express)。该联盟成立的目的旨在推动Chiplet接口规范的标准化,并已推出UCIe 1.0版本规范。

需要指出的是,通用芯粒互连技术(UCIe)是一个开放的芯粒互连协议,旨在芯片封装层面确立互联互通的统一标准,满足客户对可定制封装要求。通用芯粒互连技术提供了物理层和die-to-die适配器。物理层包含裸片间通信的电气信号、时钟标准、物理通道数量等规范,可以包含来自多家不同公司当前所有类型的封装选项,包括标准2D封装和更先进的2.5D封装。随着3D芯片封装的推出,UCIe标准还需不断升级,未来也将最终扩展到3D封装互连。

相比之下,国内本土半导体厂商在Chiplet这一块一直以来都比较欠缺。据了解,UCIe联盟成员共分为三个级别,分别是发起人、贡献者(Contributor)和采用者(Adopter),发起人由董事会组成并具有领导作用,贡献者和发起者公司可以参与工作组,而采用者只能看到最终规范并获得知识产权保护。

目前,UCIe联盟目前仅开放后两个会员级别申请。此前已有芯原、芯耀辉、芯和半导体、芯动科技、芯云凌、长芯存储、长电、超摩科技、奇异摩尔、牛芯半导体、OPPO等多家大陆企业先后宣布加入UCIe行业联盟,随着中国Chiplet生态圈不断壮大,阿里巴巴也在今年8月入选了董事会成员,标志着UCIe进入一个新的里程碑。

有人认为,Chiplet对中国解决先进芯片技术瓶颈具有重要意义,是中国市场换道超车重要技术路径之一。不过,清华大学教授魏少军却指出,Chiplet处理器芯片是先进制造工艺的“补充”,而不是替代品。“其目标还是在成本可控情况下的异质集成。”清华大学集成电路学院院长吴华强也表示,Chiplet不是先进芯片制造的替代品,但它们可能有助于中国建立“战略缓冲区”,提高本地的性能和计算能力,以制造用于数据中心服务器芯片。

部分巨头推出Chiplet相关产品

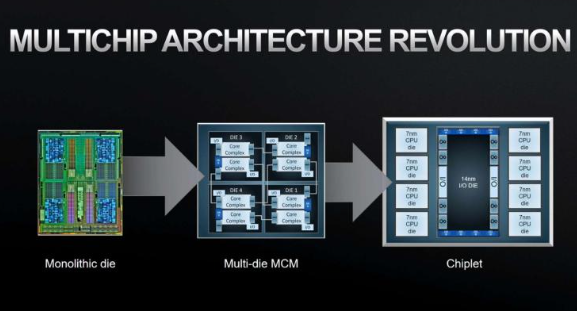

值得一提的是,小芯片Chiplet技术的落地并非是厂商们的空谈,像英特尔、AMD、ARM等均已经推出了Chiplet小芯片架构。

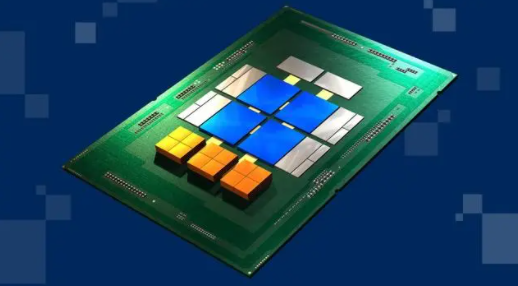

英特尔在2021年架构日时就披露了有关其下一代至强可扩展平台的功能,其中之一是向tiled架构的转变。英特尔将通过其快速嵌入式桥接器组合四个 tile/chiplet,从而在更高的内核数下实现更好的CPU可扩展性。此举也跟其他公司一样,通过“更小的核心”或“连接在一起的单个chiplet”这两种途径之一,来实现更多的服务器平台核心数量。

(基于Chiplet技术的芯片结构示意 图源:英特尔)

此前,AMD曾推出基于台积电3D Chiplet封装技术的服务器处理芯片。在今年11月,AMD正式发布了采用RDNA3架构的新一代旗舰GPU——RX7900XTX和RX7900XT。AMD表示,这是公司首度在GPU产品中采用小芯片(Chiplet)技术,即台积电的“3D Fabric”技术,也是全球首个导入Chiplet技术的游戏GPU。与使用更传统GPU设计的RDNA2相比,该款产品拥有多达580亿个晶体管,每瓦特性能提升了54%,并且提供高达61TFLOP的算力;

(AMD的Chiplet设计 图源:AMD)

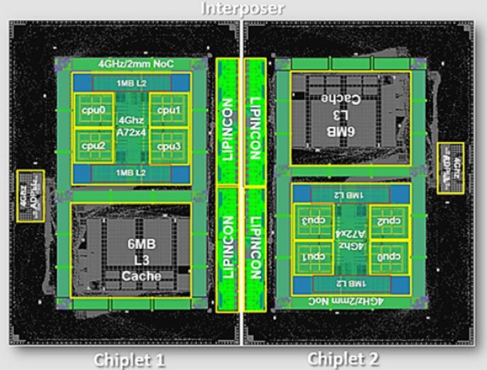

同样,在2019年美国圣塔克拉拉举办的开放创新平台论坛上,知名IP大厂Arm与台积电共同发表业界首款采用台积电先进CoWoS封装解决方案并获得硅晶验证的7nm小芯片Chiplet系统,其中内建Arm多核心处理器。据悉,这款小芯片系统成功展现出结合了7nm FinFET制程及4GHz Arm核心所打造出的高效能运算的系统单芯片(SoC)关键技术,结合了台积电创新的先进封装技术与Arm架构卓越的灵活性及扩充性,为将来生产就绪的基础架构SoC解决方案奠定绝佳基础。

(图片来源:台积电)

GPU、FPGA市场应用潜力巨大

目前Chiplet已经有少量商业应用,并吸引广大国际芯片厂商投入相关研发,在当前SoC遭遇工艺节点和成本瓶颈的情况下,Chiplet有望发展成为一种新的芯片生态。根据市场研究机构Omdia(原IHS)的预测,2024年Chiplet市场规模将达到58亿美元,而到2035年则将达到570亿美元。

其中,Chiplet在GPU、FPGA这两个有着高算力特点发热领域应用潜力巨大,具备芯片设计能力的IP供应商更有机会脱颖而出。但与此同时,Chipet未来充满机遇的同时也有挑战存在,技术层面上Chiplet面临着连接标准、封装检测、软件配合等几方面的挑战。

在连接标准上,不同供应商的Chiplet接口标准不同,比如OpenCAPI、Gen Z、CCIX、CXL等等。因此需要有统一的标准将不同制程/材质的die连接组成一个系统;封装检测方面,芯片间支持的带宽大小不同对应了不同的封装技术,选择封装技术的时候需要综合考虑成本和连接性能。在检测方面,Chiplet需要在封装前对裸片(Die)进行测试,相较于测试完整芯片难度更大,尤其是当测试某些并不具备独立功能的Chiplet时,测试程序更为复杂;软件配合方面,Chiplet的设计制造需要EDA软件从架构到实现再到物理设计全方位进行支持,另外各个Chiplet的管理和调用也需要业界统一的标准。

相关阅读:

- 传西数/铠侠重启合并谈判! 2023-01-05

- 2022年半导体行业十大并购! 2023-01-04

- 中国芯片独角兽50强 2023-01-04

- 苹果市值一夜蒸发5345亿元 2023-01-04

- 2022年半导体行业十大技术趋势! 2023-01-03

图片新闻

活动日程

- 2023-07-11

-

直播活动

09:30 -09:50

ADI携工业、汽车两大领域多款特色方案亮相慕尼黑电子展 -

直播活动

10:10 -10:30

慕尼黑电子展ITECH展台全景直播 -

直播活动

10:30 -10:50

金升阳-无忧电源·一站式电源解决方案 -

直播活动

11:00 -11:20

新一代模块化工业连接器解决方案 -

直播活动

11:30 -12:00

立讯技术“轻有源”系列解决方案 -

直播活动

14:00 -14:20

润石车规级芯片介绍 -

直播活动

14:40 -15:10

荣湃半导体巡展专访直播 -

直播活动

15:40 -16:00

安费诺携热门应用,带您“智”游慕尼黑电子展 -

直播活动

16:15 -16:35

慕尼黑电子展DigiKey展台全景直播