对标AMD、Intel!中国首个小芯片标准发布

导读: 在近期激烈的全球竞争中,国产芯片产业迎来一项重要利好,中国首个原生Chiplet 技术标准正式审定发布!在12月16日举办的“第二届中国互连技术与产业大会”上,由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布

在近期激烈的全球竞争中,国产芯片产业迎来一项重要利好,中国首个原生Chiplet 技术标准正式审定发布!

在12月16日举办的“第二届中国互连技术与产业大会”上,由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布。

对中国芯片产业而言,该团体标准是中国首个小芯片(Chiplet)技术标准,意义十分重大,这无疑是一大好消息。

小芯片(Chiplet)技术到底是什么?

所谓的小芯片(Chiplet)技术,在近两年里收到了业内的热烈关注和探讨。

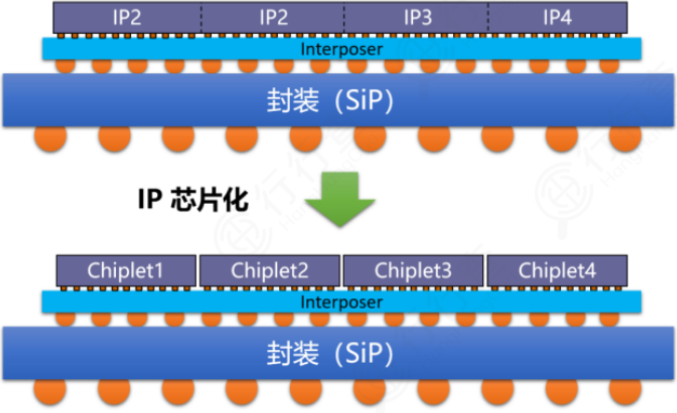

小芯片Chiplet又被称为“芯粒”,Chiplet将复杂芯片拆解成一组具有单独功能的小芯片单元die(裸片),通过die-to-die的结构将模块芯片和底层基础芯片封装组合在一起。

Chiplet的主要优势包括:

1.可以大幅提高大型芯片的良率;

2.可以降低设计的复杂度和设计成本;

3.还能降低芯片制造的成本。

为什么小芯片被这么多企业重视呢,原因是因为小芯片Chiplet架构在制程工艺难以进步的情况下,可以实现晶体管密度的突破,因此对于半导体行业来说非常重要。

早在2010年,蒋尚义先生提出通过半导体公司连接两颗芯片的方法,区别于传统封装,定义为先进封装 。

2015年Marvell创始人之一周秀文(Sehat Sutardja)博士曾提出Mochi(Modular Chip,模块化芯片)架构的概念,这是芯粒早期雏形。

而AMD是率先将芯粒技术大规模应用于商业产品的公司之一,在第三代锐龙(Ryzen)处理器上AMD便是复用了第二代霄龙(EPYC)处理器的IO Chiplet。直到2019年,国内华为等公司也在产品中使用芯粒技术。

在2022年举办的基金委双清论坛上,孙凝晖院士、刘明院士、蒋尚义先生等讨论提出了“集成芯片”概念,也是对芯粒集成芯片的概括和定义。不过,网上也有一些值得关注的观点。清华大学魏少军教授指出,Chiplet处理器芯片是先进制造工艺的“补充”,而不是替代品。“其目标还是在成本可控情况下的异质集成。”

那么此次国内审定发布的《小芯片接口总线技术要求》中都讲了哪些内容呢?

据悉,《小芯片接口总线技术要求》描述了 CPU、GPU、人工智能芯片、网络处理器和网络交换芯片等应用场景的小芯片接口总线(chip-let)技术要求,包括总体概述、接口要求、链路层、适配层、物理层和封装要求等。

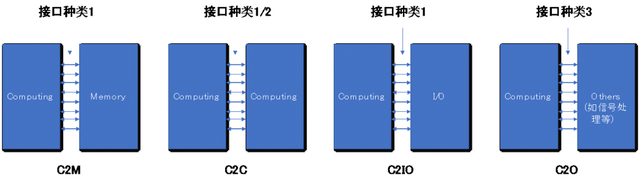

据介绍,小芯片接口技术有以下应用场景:

·C2M (Computing to Memory),计算芯片与存储芯片的互连。

·C2C (Computing to Computing),计算芯片之间的互连。两者连接方式:

·采用 并行单端 信号相连,多用于 CPU 内多计算芯片之间的互连。

·采用 串行差分 信号相连,多用于 AI、Switch 芯片性能扩展的场景。

·C2IO (Computing to IO),计算芯片与 IO 芯片的互连。

·C2O (Computing to Others),计算芯片与信号处理、基带单元等其他小芯片的互连。

此标准列出了并行总线等三种接口,提出了多种速率要求,总连接带宽可以达到 1.6Tbps,以灵活应对不同的应用场景以及不同能力的技术供应商,通过对链路层、适配层、物理层的详细定义,实现在小芯片之间的互连互通,并兼顾了 PCIe 等现有协议的支持,列出了对封装方式的要求,小芯片设计不但可以使用国际先进封装方式,也可以充分利用国内封装技术积累。

(《小芯片接口总线技术》标准概况图)

换个角度来看,小芯片Chiplet技术其实就是模块化的芯片技术,可以由多个不同制程、架构、功能的小芯片堆叠出全功能芯片,在半导体行业已经极为常见。此次中国发布原生Chiplet小芯片标准,无疑将推动本土半导体芯片这一领域的发展。

单片式SOC与Chiplet SOC的比较

Chiplego首席技术顾问曾在《揭秘后摩时代芯片产业方向:Chiplet技术》一文中提到,在不考虑制造成本的情况下,人们总是认为单片SOC可以比Chiplet SOC提供更好的性能和功耗。事实上,单片SOC中每个模块都能以最小的延迟进行通信,这使得前者比Chiplet SOC的性能更好。然而,如果把制造成本作为一个芯片设计目标,那么有些单片SOC设计可能会成为一个不可能完成的任务。

他以AMD的64核Chiplet芯片设计为例:在7nm技术中,CPU Chiplet尺寸约为81mm^2;在12nm技术中,I/O芯片的尺寸约为125mm^2。如果采取单片设计方法,单片SOC的裸片尺寸应该在700mm^2到800mm^2之间。

(Chiplet与SoC的区别)

而在目前的EUV曝光机中,光掩模版尺寸约为858mm^2。在未来的High-NA EUV中,光掩模版可能会小于450mm^2。因此,无论采用哪种情况,AMD 64核SOC的单片设计都难以生产,即使单片设计能提供卓越的性能和功耗。如果人们仍然想以单片SOC中完成64个CPU Core的设计,只有通过减少高速缓存的大小,比如缩减一半甚至更多,这样芯片尺寸就可以减少一半,单片SOC在7nm中可以达到400mm^2左右,但这种设计方案在生产成本方面并不合理。总而言之,在一个系统中,不同的功能和特性所需要的工艺技术往往是不兼容的。例如,DRAM和RF工艺技术与逻辑SOC就不兼容。在这种情况下,单片SOC是不可能的。如果想把这些功能块集成到一个封装中,Chiplet SOC是唯一的解决方案。

相关阅读:

- 传西数/铠侠重启合并谈判! 2023-01-05

- 2022年半导体行业十大并购! 2023-01-04

- 中国芯片独角兽50强 2023-01-04

- 苹果市值一夜蒸发5345亿元 2023-01-04

- 2022年半导体行业十大技术趋势! 2023-01-03

图片新闻

活动日程

- 2023-07-11

-

直播活动

09:30 -09:50

ADI携工业、汽车两大领域多款特色方案亮相慕尼黑电子展 -

直播活动

10:10 -10:30

慕尼黑电子展ITECH展台全景直播 -

直播活动

10:30 -10:50

金升阳-无忧电源·一站式电源解决方案 -

直播活动

11:00 -11:20

新一代模块化工业连接器解决方案 -

直播活动

11:30 -12:00

立讯技术“轻有源”系列解决方案 -

直播活动

14:00 -14:20

润石车规级芯片介绍 -

直播活动

14:40 -15:10

荣湃半导体巡展专访直播 -

直播活动

15:40 -16:00

安费诺携热门应用,带您“智”游慕尼黑电子展 -

直播活动

16:15 -16:35

慕尼黑电子展DigiKey展台全景直播